HWL News Bot

News

Thread Starter

- Mitglied seit

- 06.03.2017

- Beiträge

- 117.027

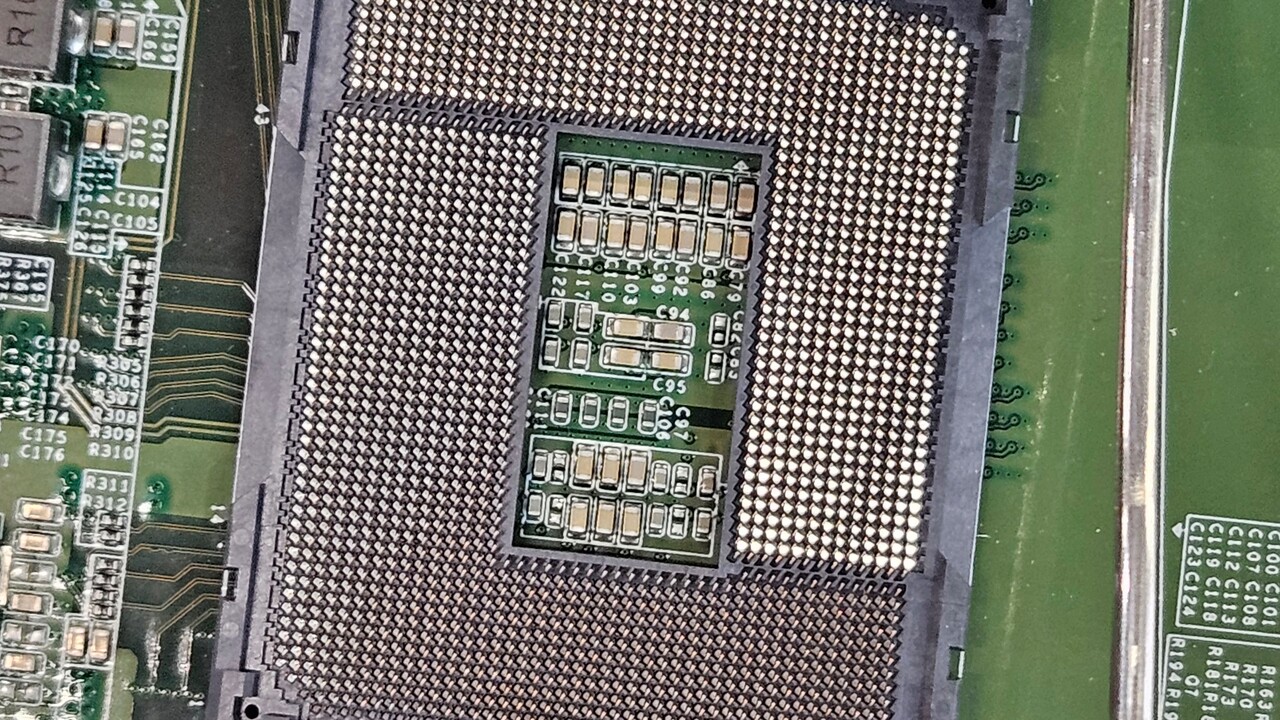

Bereits mit dem ersten Auftauchen der X3D-Technologie, die AMD dann später als 3D V-Cache vermarktet hat und inzwischen zu einem wichtigen Merkmal in AMDs Prozessor-Portfolio geworden ist, deutete sich an, dass AMD die Größe des Caches über ein Stapeln mehrerer Schichten skalieren kann. In der nächsten Generation der Ryzen- und EPYC-Prozessoren soll es nun soweit sein. Dies berichtet Moore's Law is Dead, dessen Meldungen meist mit Vorsicht zu genießen sind, der in einigen Details aber auch immer mal wieder richtig liegt.

... weiterlesen

... weiterlesen

hmmm....... artikel von gestern

hmmm....... artikel von gestern