Werbung

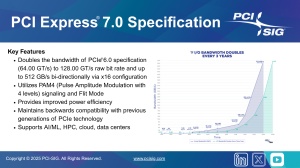

In der vergangenen Woche hat die PCI-SIG die finalen Spezifikationen für die nächste PCI-Express-Generation 7.0 veröffentlicht und verspricht darin eine erneute Verdopplung gegenüber dem Vorgänger 6.0. Mit der Version 7.0 fortgesetzt, wird die Anwendung der Pulsamplitudenmodulation PAM-4, was eine der wesentlichen Änderungen gegenüber dem aktuell verwendeten 5.0-Standard ist.

PCI-Express 7.0 ermöglicht die Übertragung von 128,0 GT/s, was in einer Übertragungsrate von 15,125 GB/s auf einer Lane resultiert. Auf die häufig verwendeten 16 Lanes angewendet landen wir somit bei 242 GB/s, bzw. 484 GB/s bidirektional und ohne den Protokoll-Overhead. Nominell sind es bei 16 Lanes 512 GB/s.

Bis wir die erste PCI-Express-7.0-Hardware im Produktiveinsatz sehen, dürfte noch einige Zeit vergehen. Im kommenden Jahr wird mit den ersten Serverplattformen gerechnet, die auf PCI-Express 6.0 setzen werden. Bereits mit PCI-Express 5.0 zeigte sich im Serverumfeld, dass eine entsprechende Validierung der Plattformen viel Zeit und Arbeit in Anspruch nimmt. Dies war eine der Komponenten, die zur Verzögerung der vierten Xeon-Scalable-Prozessoren Sapphire Rapids geführt hat.

Ob es mit PCI-Express 6.0 und 7.0 nun einfacher wird, die Plattformen zu validieren, bleibt eine spannende Frage. 128 oder gar 192 PCI-Express-Lanes aus einem oder zwei Sockel an die Steckplätze und Erweiterungsstecker zu bringen, scheint jedenfalls kein triviales Unterfangen zu sein.

Im Endkundenbereich scheinen die Hersteller ohnehin bereits auf die Bremse zu steigen. Einerseits haben AMD und Intel bei den Ryzen- und Core-Prozessoren noch keinerlei Ambitionen hier bald auf PCI-Express 6.0 wechseln zu müssen (oder zu können, falls der Produktzyklus passt) und andererseits sorgt das teure Platinenlayout nebst Validierung für steigende Kosten. Dabei sind die Preise bei den Mainboards in den vergangenen Jahren ohnehin deutlich gestiegen.

Aber auch die Hersteller der Controller, zum Beispiel für die SSDs, sind zurückhaltend. Gegenüber Tom's Hardware äußerte sich der CEO von Silicon Motion dergleichen, dass ein Tape-Out eines SSD-Controllers für PCI-Express 5.0 in 6 nm bereits 16 bis 20 Millionen US-Dollar. In 4 nm sollen es sogar 30 bis 40 Millionen US-Dollar sein. Die Entwicklung des eigentlichen Controllers ist darin noch nicht enthalten. Wegen der hohen Kosten suchen die Controller-Hersteller immer wieder nach Alternativen zu TSMC, wo die meisten Controller hergestellt werden. Samsung könnte hier eine Alternative sein, ist in der Fertigung aber nicht so weit fortgeschritten. Samsung selbst fertigt seine eigenen Controller aber dort. Innogrit, Phison und auch Silicon Motion sind ständig auf der Suche nach dem besten Prozess.

Bis 2030 erwartet Silicon Motion nicht, dass im Endkundenbereich der Wechsel von PCI-Express 5.0 auf 6.0 vollzogen werden kann. Bis dahin sollen die fast 16 GB/s für vier PCI-Express-5.0-Lanes ausreichend sein. Anders sieht dies im Rechenzentrum ein. Hier kann die Übertragungsrate gar nicht hoch genug sein, bzw. verdoppelt sich diese, ohne dass zugleich die Leistungsaufnahme verdoppelt wird, wird dies als deutlicher Zugewinn in der Effizienz angesehen. Mit den zukünftigen PCI-Express-6.0-SSDs sollen die Controller zudem noch Aufgaben übernehmen, die aktuell noch beim Host-Prozessor liegen. Damit soll das Gesamtsystem entlastet und schneller werden.

PCI-Express 6.4 und 7.0 für optische Verbindungen

Um PCI-Express-Signale effizient und über weitere Strecken zu übertragen, sieht der Standard eine optische Übertragung vor. Zusammen mit der Spezifikation für PCI-Express 7.0 wurden die Standards PCIe 6.4 und 7.0 festgezurrt. In den Spezifikationen für die PCIe Optical Interconnect Solutions vorgesehen sind und Optical Aware Retimer.

Das Pooling von NVMe-Speicher dürfte eine Hauptanwendung der optischen Übertragung eines PCI-Express-Signals sein. Aber natürlich lassen sich auch andere PCI-Express-Geräte darüber anbinden. KI-Server dürften die ersten sein, die auf eine solche Übertragung setzen werden.