Niko199112

Experte

- Mitglied seit

- 08.08.2021

- Beiträge

- 1.505

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: this_feature_currently_requires_accessing_site_using_safari

Das Gerücht als falsch zu entlarven ist einfach: N2X steht in TSMCs Roadmap erst für 2027:Zen6 möglicherweise mit über 7ghz:

AMD Ryzen X mit 7 GHz: Ganz wilde Gerüchte um Zen 6

Ganz wilde Gerüchte zu AMDs Zen 6 und Ryzen X/10000 machen jetzt die Runde und sprechen von Taktfrequenzen von mehr als 7 GHz.www.pcgameshardware.de

Das Problem von großen Caches ist, dass deren Verwaltung auch aufwendiger wird und damit im Prinzip mehr Zeit braucht. Die Hitrate steigt außerdem nicht proportional zur Größe des Caches und damit bringt mehr Cache ab einer bestimmten Größe immer weniger und wenn die Verwaltung dann noch länger dauert, dann kann der große Cache sogar langsamer als ein kleinerer sein. Dazu kommen die Kosten und auch die Leistungsaufnahme, SRAM braucht ja auch einiges an Strom.Gestapelter X3D-Cache für den Desktop? Eher nicht, das sehe ich nur für EPYC. Da wird von den leakern wieder alles in einen Topf geworfen.

Eben.Na ja, Hauptsache Klicks generiert.

N3P wäre möglich, aber traditionell nutzt AMD die X Variante (bei N5 wurde diese noch HPC genannt), nicht die P Variante der Prozesse. N2P, welches ja nach anderen Gerüchten mit Nova Lake in Verbindung gebracht wird, wäre zeitlich extrem knapp und dann ist es eine Frage der Volumen, denn die Kapazitäten steht ja nicht gleich zu Beginn der Fertigung massenhaft zur Verfügung, die werden dann erst aufgebaut, wenn der Prozess rund läuft. Für die kompakten Zen6c Kerne braucht man die P Variante des Prozesses auch nicht, da die sowieso keine hohen Taktraten haben.

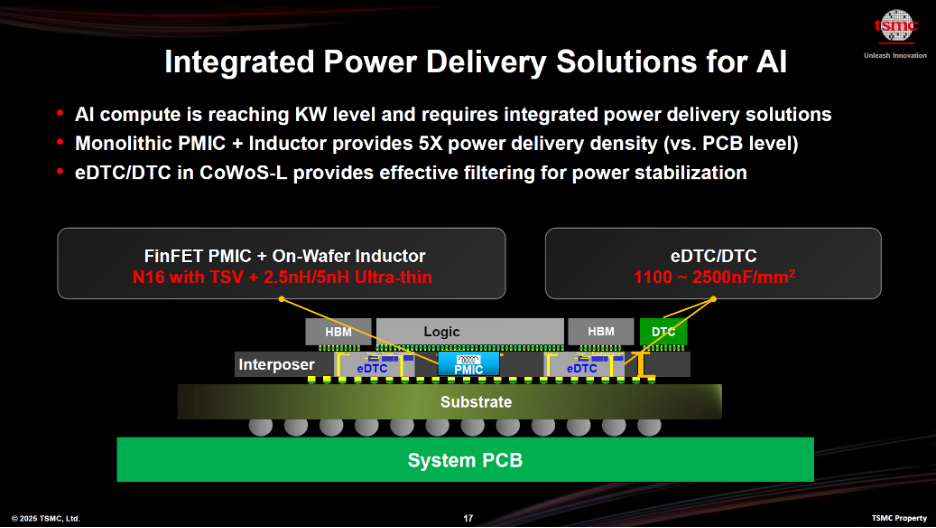

Vom April 2025 vom TSMC Tech Symposium 2025:Von wann oder woher ist denn deine Roadmap?

Nachmal: Die G sind die APUs mit einem monolithischem Die und nicht mit dem Chiplet Design der CPUs, seit den Zen2 RYZEN 3000. Die CPU teilen sich schon seit den ersten Zen die CPU Chiplets mit den EPYC CPUs und zwar die großen Classic Kerne, nicht die kompakten c Kerne, denn deren Die hat schon jetzt mehr als 8 Kerne, aber man kann da keinen zusätzlichen V-Cache aufsetzen. Daher wird AMD auch zukünftig diese Dies nehmen, vielleicht gemischt einen Die mit den großen Kernen und einen Die mit den kompakten c Kernen, aber selbst daran glaube ich eher weniger.Aber jetzt bei der Ryzen 9000G Serie sollen die Zen5c Kerne ja durch die Bank kommen. Und deswegen gehe ich eben davon aus, da man vielleicht auch bei der Ryzen 10000 Serie auf eine ähnliche Strategie setzen könnte. 12 vollwertige Zen6 Kerne und noch dazu 3D Cache klingen für mich zu schön um wahr zu sein.

Ich weiß nicht... Hast du mit der Zeit irgendwelche Resistenzen entwickelt oder gibt es bei dir Inselbegabungen die hier nicht greifen? Der Tape-out von Venice ist durch. Das sind Classic. Venice sind auch die CCDs von Ryzern. Der Tape-out war in N2.Zen6 (Classic) Kerne werden wahrscheinlich in N3X gefertigt,

Wo steht das? Bisher gibt es von AMD zu Venice die Folie mit 256 Kernen, was dann keine Classic Venice sind, sondern die Compact mit den Zen6c Kernen und die Zen6x Kernen werden in N2 gefertigt. Da aber beide EYPC Varianten einfach nur Venic genannt werden und AMD auch in solche Folien nicht zwischen Zen6 und Zen6c unterscheiden, gibt es eben diese Missverständnisse die zu den Clickbait "Leaks" einladen. Das hatten wir doch alles bei Zen5 schon, da haben auch manche darauf bestanden, dass die in N3 gefertigt werden, was aber eben nur für die Zen5c Kerne stimmt.Der Tape-out von Venice ist durch. Das sind Classic. Venice

Auf der Folie steht Venice mit 96 classic oder 256 compact. Jetzt müsste man nur herausfinden was es da impliziert haben sollte, daß der Tape-out die compact-Version betraf?Wo steht das? Bisher gibt es von AMD zu Venice die Folie mit 256 Kernen, was dann keine Classic Venice sind

Oder umgekehrt, was impliziert hat, dass es die Classic Zen6 Kerne waren?Jetzt mpsste man nur herausfinden was da impliziert haben sollte, daß der Tape-out die compact-Version betraf?

Dabei hatte ich doch schon im Post #18 noch einen zitiert:Rein theoretisch, zugegeben, kannst du ggf. Recht behalten, aber du bist der einzige den ich im globalen Netz finde

Techpowerup halte ich für weitaus seriöse als die meisten Seiten die über jedes Gerüchte berichten, selbst wenn es wie das 7GHz Gerüchte auf den ersten Blick als Fake zu entlarven ist. Aber denen geht es nur um die Klicks und die bekommt man für die fantastisch klingenden News besser als für realistische News.

Das ist wie beim Fußball. Du kannst den Ball nicht direkt wieder zurückspielen, ohne ihn zu berührenOder umgekehrt, was impliziert hat, dass es die Classic Zen6 Kerne waren?

Es wirkt sich NULL auf die Einkaufsplanung der Mitlesenden, ob man Zen6 Richtung N3 oder N2 schlabbert. Es ist quasi wayne...

Es wirkt sich NULL auf die Einkaufsplanung der Mitlesenden, ob man Zen6 Richtung N3 oder N2 schlabbert. Es ist quasi wayne...Also halten wir fest: Es ist reine Vermutung und gibt keinerlei Hinweis ob es Zen6 Classic oder Dense Zen6c war.Du kannst den Ball nicht direkt wieder zurückspielen, ohne ihn zu berühren

Man kann davon ausgehen, dass die N3X Fertigung günstiger als N2 sein dürfte.Ein N3X wird für viele finanziell attraktiver sein als N2.

Bein N5 nannte sich der Prozess noch N5HPC und seit N4 nennt sich die Variante die AMD für die Dies der Kern Chiplets der Desktop CPUs und entsprechenden EPYC nutzt, nun die X Variante, die zeitlich auch immer passend zum Erscheinen der CPUs erscheint. Die steht nun offenbar auch anderen Kunden zur Verfügung, aber wer sollte sie sonst brauchen, außer vielleicht Intel, aber Intel hat eine andere Variante gewählt. Vielleicht ist die X Variante doch nur exklusiv für AMD, praktisch ist sie es ja sowieso, da kein GPU und kein Smartphone SoC so einen hohen Takt braucht, da begrenzt die Leistungsaufnahme sowieso die Frequenz, eben genau wie bei EYPC Dense.Es wäre nicht das erste Mal, falls AMD nicht den von der Stange, sondern einen custom node bekommen würde...

Scheinbar nimmst du jedes Gerücht ernst. Traurig, wenn jemand gar kein kritisches Denken entwickelt hat! Damit ist hier Schluss für mich, denn mit so jemandem ist es sinnfrei diskutieren zu wollen, da er einfach zu viel Blödsinn aus dem Netz aufsaugt und für bare Münze nimmt.bis Titan Lake da ist. (und dieser Blödsinn mit P und E in einer CPU endlich wieder aufhört)

Also ich haben nur Aktien europäischer, vor allem deutscher Unternehmen, aber keine US Aktien.falls du keine Aktien von Intel hast...)

Das die Quellenlage gleich ist, stimmt ja nur in dem Sinne, dass wir hier alle auf Informationen angewiesen sind, die offen im Internet stehen. Der Unterschied ist, welche dieser Informationen man kennt und wie man diese dann auswertet und da haben so manche Leute bei der Fähigkeit die man als "Lesen und Verstehen" bezeichnet, mehr Herausforderungen als andere, gerade auch wenn die Informationen nicht in der Muttersprache vorliegen. Wer dann auf Übersetzungen angewiesen ist, hat schon mal eine Fehlerquelle mehr eingebaut. Dann kommt der wichtigste Punkt, nämlich diese Informationen zu bewerten, dabei ist es extrem wichtig auch die Quelle der Informationen einschätzen zu können, denn Fake News und Click Bait sind leider Alltag im Internet und die Informationen am Ende sinnvoll zu verknüpfen.Und das immer üppiges Wissen darüber - bei gleicher Quellenlage - welche Gerüchte wahrscheinlicher sind und welche überhaupt nicht.

Ja, aber sicher ist dies nur für die Dense VarianteZen6 kommt in N2.