Werbung

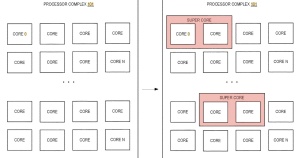

Das Konzept ist nicht neu und wurde in der Vergangenheit für einzelne Funktionseinheiten immer wieder verwendet: Die Rede ist von konfigurierbaren CPU-Kernen, die sich gewisse Ressourcen teilen, um so in bestimmten Anwendungen eine höhere Rechenleistung zu erreichen. Intel hat vor einigen Wochen in gleich mehreren Ländern ein Patent "Software-defined Super Cores" (SDC) eingereicht. In den USA läuft dies unter der Patentanmeldung US20250217157A1.

Laut der gezeigten Schaubilder und Beschreibung des Patents sollen zwei Kerne zusammenarbeiten, um einen einzelnen Thread schneller verarbeiten zu können. Spezielle Instruktionen - sogenannte "Flow Control Instructions" – werden dazu in eine Single-Threaded-Anwendung geschrieben, damit der Scheduler weiß, welche Abschnitte er parallelisieren kann. Der Overhead für die Aufteilung auf mehrere Kerne soll relativ gering sein – sowohl auf Seiten der Software und des Codes, als auch auf Seiten der Hardware in Form spezieller Schaltungen (das sogenannte SDC Interface) in den einzelnen Kernen.

Der Ansatz der SDCs könnte Intels aktuelles Problem adressieren: Seit Alder Lake bietet Intel in seinen Desktop- und Mobil-Prozessoren sowohl die schnellen Performance-Kerne als auch die sparsameren und effizienteren Efficiency-Kerne an. Ein Cluster mit vier E-Kernen belegt in etwa so viel Chipfläche wie ein P-Kern und mit inzwischen bis zu 16 E-Kernen im Desktop konnte Intel die Multi-Threaded-Leistung immer weiter steigern und bietet auch hinsichtlich der Effizienz einen guten Ansatz. Bei den P-Kernen jedoch drehte Intel für eine hohe Single-Threaded-Leistung derart an der Takt- und Spannungsschraube, dass es sogar zu Stabilitätsproblemen uns Ausfällen der Chips gekommen ist.

Die Software-defined Super Cores könnten für Intel ein Lösungsansatz, bzw. ein Mittelweg sein. Einerseits könnte Intel seine P-Kerne in dieser Form optimieren, dass diese ohne extreme Takt- und Spannungsvorgaben dennoch eine hohe Leistung erreichen. Andererseits könnten auch die E-Kerne per SDC in der Leistung verbessert werden.

Anleihen aus der Vergangenheit und Gegenwart

In der Konzeption zahlreicher Chip-Designs und Architekturen kommt der gemeinsame Einsatz mehrerer Recheneinheiten eines oder mehrerer Kerne bereits zum Einsatz. Das grundsätzliche Konzept dahinter nennt sich Coarse-Grain Reconfigurable Array (CGRA).

Für die Zen-4-Architektur beispielsweise sah AMD für die Ausführung einer AVX-512-Instruktion in Form zweier 256-Bit-Berechnungen vor. Mit der Zen-5-Architektur wurde der Datenpfad der Fließkomma-Einheiten auf 512 Bit erweitert, so dass AVX-512-Instruktionen nun in voller Breite und in einem Taktzyklus berechnet werden können.

Ein anderes Beispiel sind die Kerne der Bulldozer-Architektur von AMD. Hier wurden zwei Kerne in einem Modul eng miteinander gekoppelt. So besaß jedes Modul zwei 128-Bit-Gleitkommaeinheiten (FPUs), die bei Bedarf zu einer 256-Bit-breiten Gleitkommaeinheit kombiniert werden konnten.

Nicht bekannt ist, ab welcher Architektur Intel die Software-defined Super Cores zum Einsatz bringen will.