Werbung

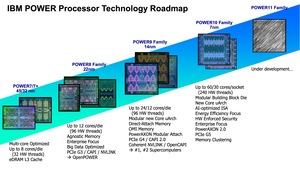

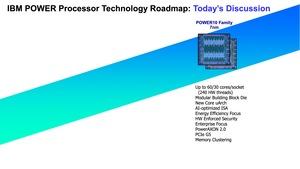

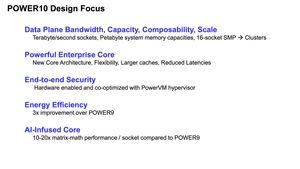

Auf der HotChips-Konferenz im August 2016 stellte IBM die POWER9-Architektur vor. Zur HotChips 32, die heute startet, präsentiert IBM den Nachfolger POWER10. Dieser ist IBMs erster in 7 nm gefertiger Prozessor, der in allen Bereichen im Vergleich zu POWER9 überarbeitet wurde und demnach auch in allen Bereichen verbessert worden sein soll. Neben der Fertigung betrifft dies die Core-Architektur, aber auch die Speicher- und I/O-Funktionen.

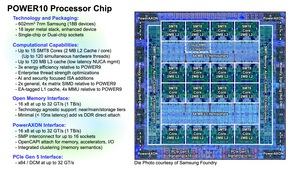

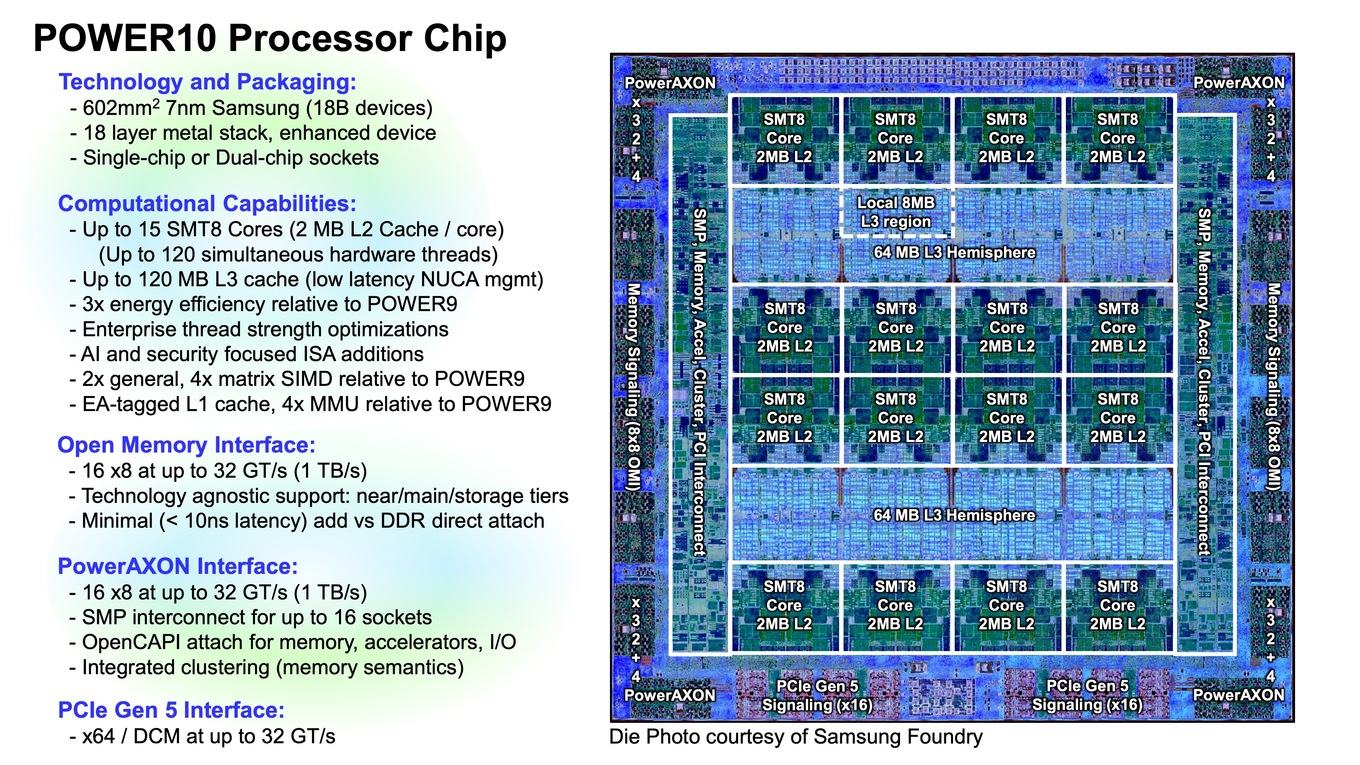

Zunächst einmal zu den wichtigen Daten eines POWER10-Prozessors: Dieser wird bei Samsung in 7 nm gefertigt und kommt auf eine Chipfläche von 602 mm². Damit ist er nicht ganz so groß wie NVIDIAs GA100-GPU, die 826 mm² groß ist und sich damit noch gerade so an den Limits der Fertigung bewegt. Die Anzahl der Transistoren eines POWER10-Prozessors liegt bei 18 Milliarden. Die GA100-GPU kommt hier auf 54 Milliarden Transistoren – nur um die Komplexität eines POWER10-Chips einmal einordnen zu können. Ein POWER10-Chip besteht aus 18 Metallschichten, was in 7 nm gefertigt im üblichen Rahmen anzusehen ist. Zusammen mit Samsung hat IBM einige spezielle Techniken in der Fertigung entwickelt, die beim POWER10 angewendet werden. Dies soll unter anderem die Leistung der einzelnen Transistoren positiv beeinflussen.

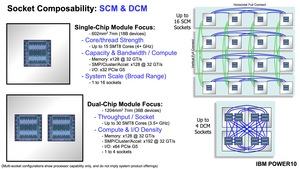

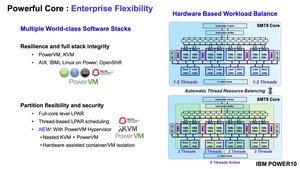

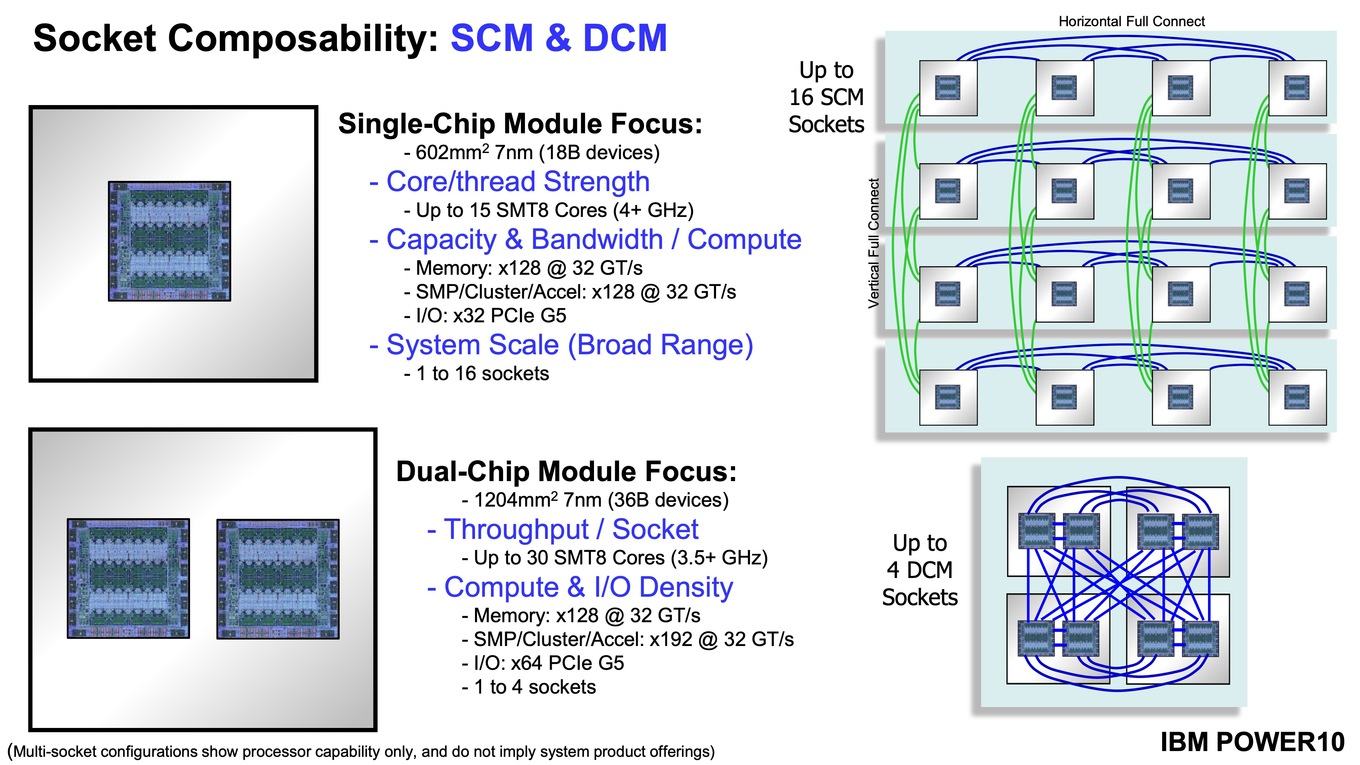

Den POWER10-Prozessor gibt es in zwei Varianten: Einmal als Single Chip Module (SCM) und einmal als Dual Chip Module (DCM). Dazu kommen wir aber noch.

Der POWER10-Chip besteht unter anderem aus 16 der neuen Kerne, allerdings werden nur 15 dieser Kerne aktiv verwendet. Jeder dieser Kerne kann per Simultaneous Multithreading (SMT) bis zu acht Threads gleichzeitig bearbeiten und dazu stehen ihm exklusiv 2 MB an L2-Cache zur Verfügung. Chipübergreifend sind zudem 120 MB an L3-Cache vorhanden.

Die Aufteilung in ein Single Chip Module (SCM) und ein Dual Chip Module (DCM) begründet IBM mit den unterschiedlichen Bedürfnissen an die entsprechenden Anwendungen. Das SCM bietet alle Interface-Optionen mit der vollen Bandbreite an und eignet sich daher für Anwendungen, bei denen eben diese hohe Bandbreiten zusammen mit der entsprechenden Compute-Leistung gefragt sind. Die 15 Kerne erreichen in der SCM-Konfiguration einen Takt von 4 GHz und mehr. Bis zu 16 Sockets in der SCM-Konfiguration können zu einem Verbund zusammengeschaltet werden und skalieren aufgrund der schnellen Anbindung auch gut.

Wenn es um die Energieeffizienz geht, sieht IBM das DCM im Vorteil. Man kann hier zwei POWER10-Chips in einem Package anbieten, wo zuvor nur ein POWER9-Prozessor seinen Platz gefunden hat. Als Multi-Chip-Module arbeitet hier sozusagen ein Chip von 1.204 mm². Die Anzahl der miteinander verbundenen Sockets wird allerdings auf vier reduziert und hinzu kommt, dass die einzelnen Prozessoren mit einem reduzierten Takt von 3,5 GHz arbeiten.

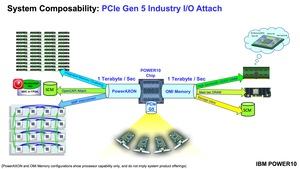

Im DCM verdoppelt sich die Anzahl der PCI-Express-Lanes. Insgesamt vorhanden sind 64 PCI-Express-5.0-Lanes, die zusammengenommen auf eine Datenrate von 1 TB/s kommen. Das Speicher-Interface bleibt mit 16 x 8 Links identisch. Das PowerAXON-Interface wird von 16 x 8 auf 16 x 12 Links vergrößert.

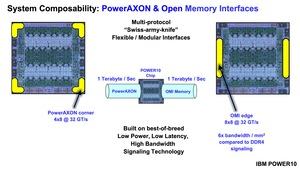

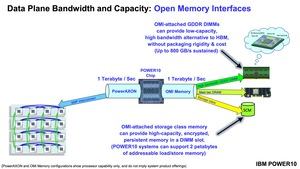

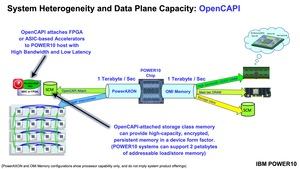

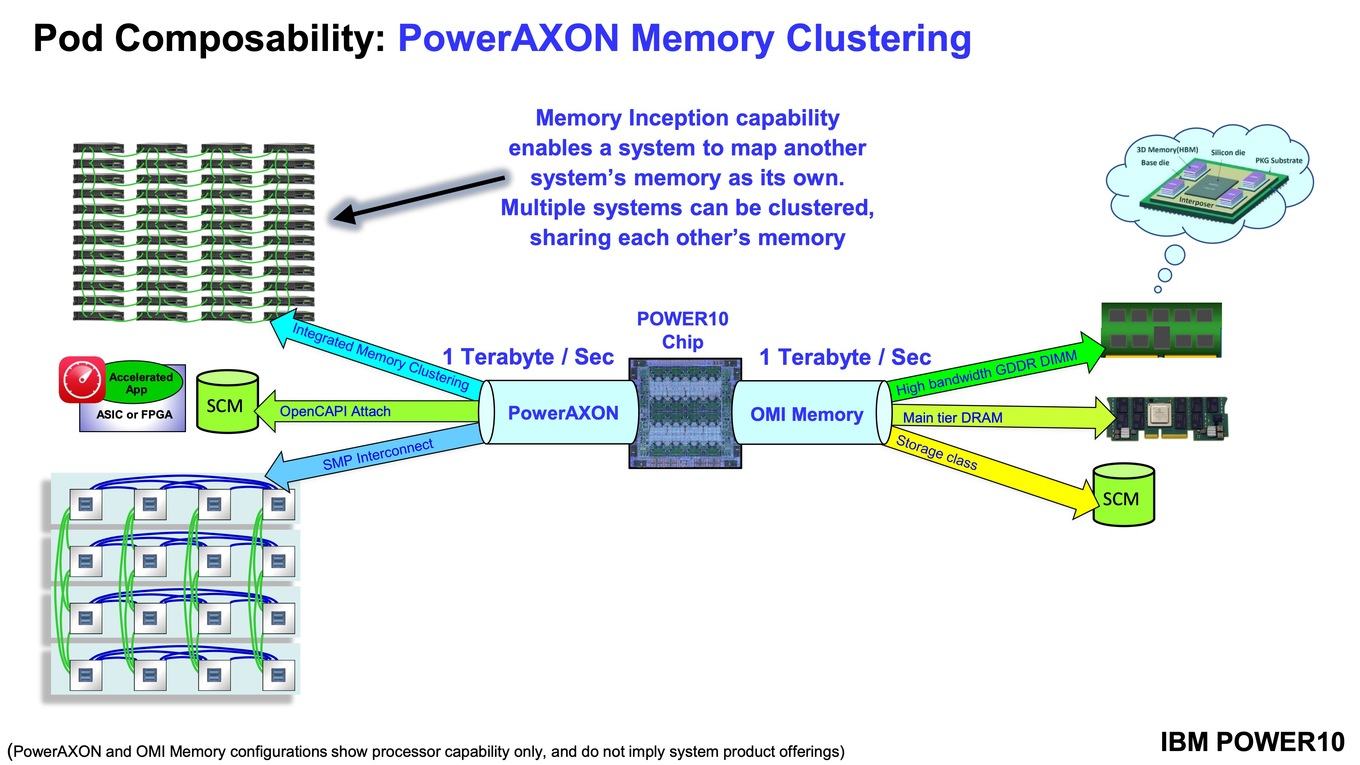

Ein wichtiger Bestandteil der POWER10-Prozessoren sind Multi-Protokoll-Interfaces PowerAXON und das Open Memory Interface (OMI). Wie bereits auf dem Chipshot zu erkennen ist, befindet sich das PowerAXON an den Ecken des Chips und das OMI links und rechts an den Rändern des Chips. Auf Seiten des PowerAXON werden 16 x 8 Links mit jeweils 32 GT/s verwendet, um POWER10-Prozessoren unter- oder andere Beschleunigerchips miteinander zu verbinden. Dazu ist PowerAXON auch zu OpenCAPI kompatibel. PowerAXON ist auch schon Bestandteil der POWER9-Prozessoren und wird hier unter anderem für die Umsetzung von NVLink verwendet.

Das Speicherinterface ist kein traditionelles DDR-Speicherinterface, sondern ein differentiales Signalinterface, welches mehrere Protokolle unterstützt. Mit 8x8 Links mit jeweils 32 GT/s bietet es auf die Chipfläche gesehen eine um den Faktor sechs höhere Bandbreite pro Quadratmillimeter im Vergleich zu DDR4.

Über das OMI können bis zu 16 DDR-DIMMs angesprochen werden. Pro Socket ist ein Speicherausbau von bis 4 TB möglich und die Speicherbandbreite liegt bei 410 GB/s. Da OMI Standard-agnostisch arbeitet, können auch anderen Standards wie eben DDR5 umgesetzt werden.

Aber nicht nur der Einsatz eines DDR-Standards ist möglich, sondern auch GDDR oder HBM können verwendet werden. Somit soll eine Speicherbandbreite von bis zu 800 GB/s ermöglicht werden. Hinsichtlich der Speicherbandbreite bewegen wir uns also in Bereichen, die GPU-Beschleuniger mit GDDR erreichen. Wird ein Storage Class Memory (SCM) verwendet, kann der Speicher sogar auf bis zu 2 PB ausgebaut werden.

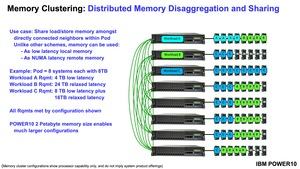

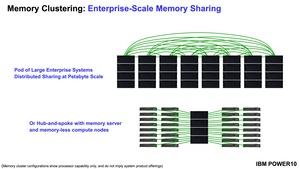

Neben dem SMP-Interconnect für die Verbindung mehrere Sockets mit POWER10-Chips bietet PowerAXON nun ein sogenanntes Memory Clustering. Dies ermöglicht es den einzelnen Prozessoren auf den Speicher eines anderen zuzugreifen – ein kohärentes Speichersystem also. Die Zugriffszeiten sollen laut IBM bei nur 50 bis 100 ns liegen. Dies ist für Speicherzugriffe über NUMA-Knoten hinweg extrem wenig.

Workloads lassen sich also über mehrere Systeme bzw. deren Speicher verteilen, was auch heute schon mit anderen Techniken möglich ist. NVIDIA bietet ein kohärentes Speichersystem über den NVLink-Interconnect. Memory Clustering macht allerdings eine Nutzung anderer Speicherbereiche möglich, ohne die meisten Nachteile (zum Beispiel die Zugriffszeiten im Bereich von Millisekunden) mitzunehmen.

| POWER9 | POWER10 | |

| Fertigung | 14 nm (GFO) | 7 nm (Samsung) |

| Transistoren | 8 Milliarden | 18 Milliarden |

| Chipgröße | 693 mm² | 602 mm² |

| Kerne | bis zu 22 | bis zu 2x 15 |

| SMT | SMT4/SMT8 | SMT4/SMT8 |

| L1-Cache (I/D) | 32/32 kB/Kern | 48/32 kB/Kern |

| L2-Cache | 512 kB/Kern | 2 MB/Kern |

| L3-Cache | 110 MB | 120 MB |

| Interfaces | DDR4-2667/DDR4-3200 OMI PowerAXON (SMP, OpenCAPI, NVLink) PCIe 4 | DDR4/DDR5 OMI PowerAXON (SMP, OpenCAPI, Memory Clustering) PCIe 5 |

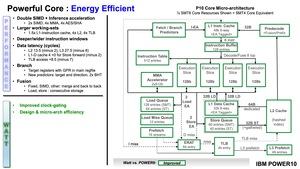

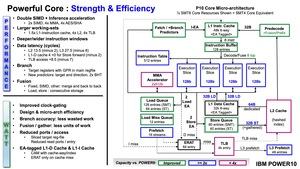

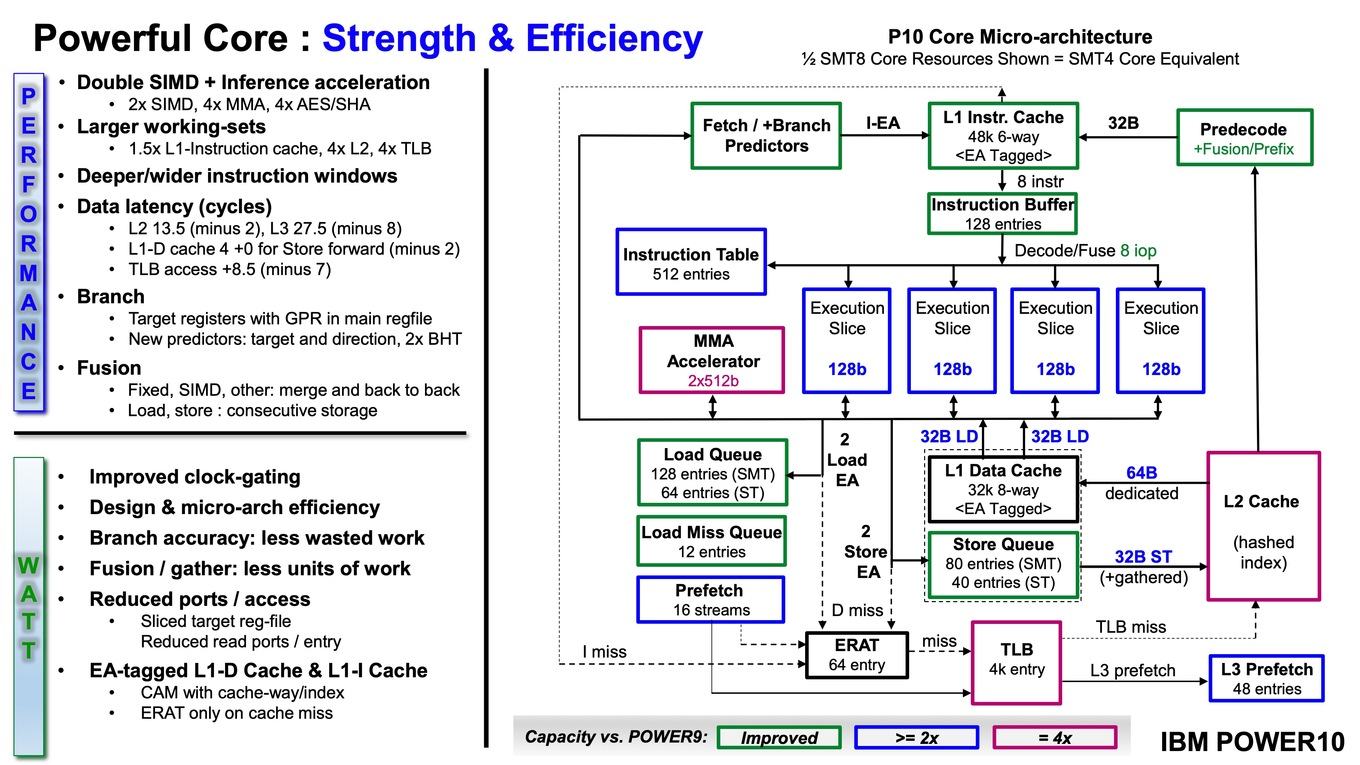

Die POWER10 Mikro-Architektur

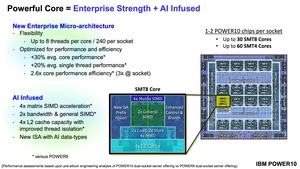

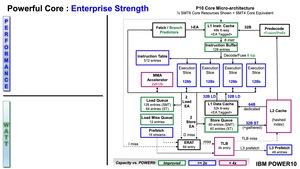

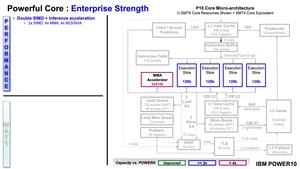

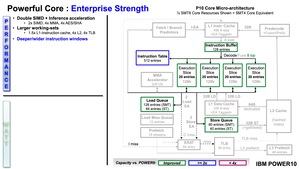

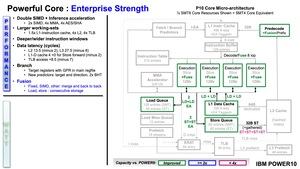

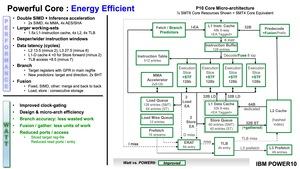

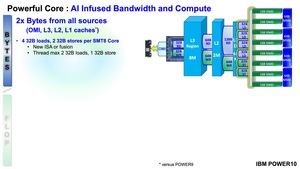

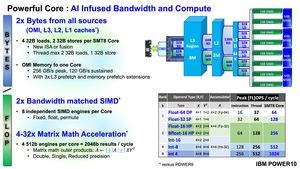

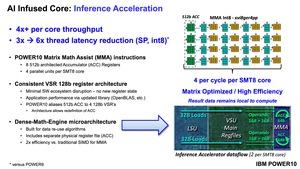

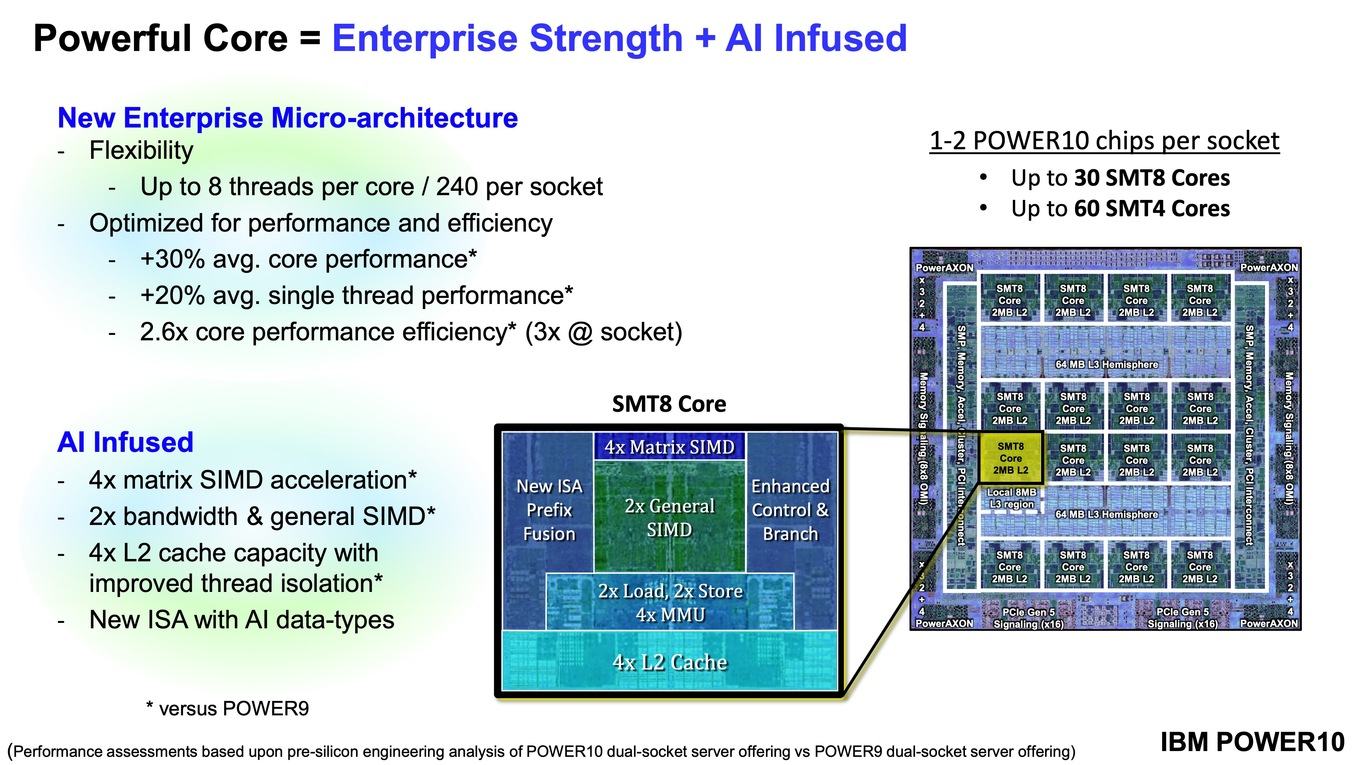

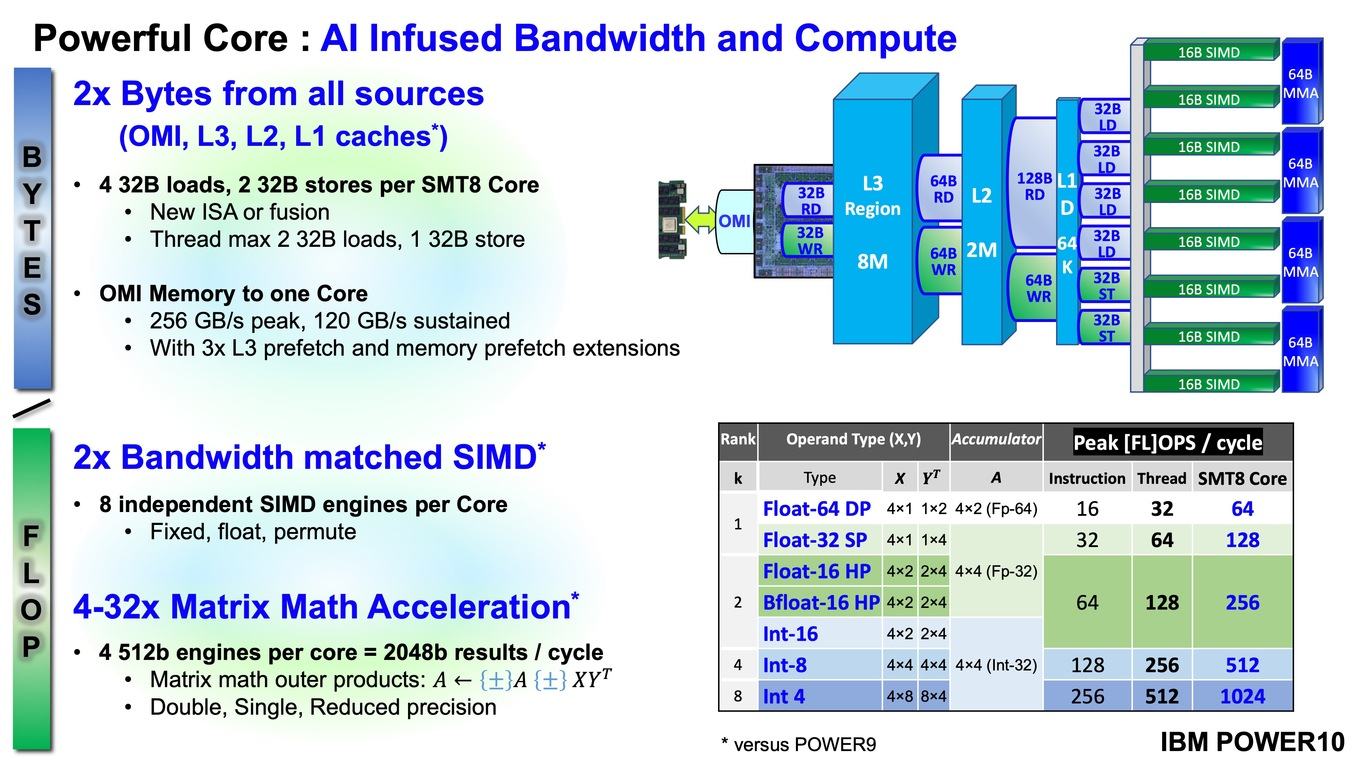

Wir haben nun schon recht ausführlich die Plattform beschrieben, wollen nun aber genauer auf die eigentliche Mikro-Architektur der POWER10-Prozessoren eingehen. Jeder einzelne SMT8-Kern besteht aus acht unabhängigen SIMD-Einheiten (Single instruction, multiple data). Deren Anzahl hat sich im Vergleich zu POWER9 also verdoppelt. Um die SIMD-Einheiten füttern zu können hat IBM die Anzahl der Load- und Store-Einheiten verdoppelt, sowie die der Memory Management Units (MMU) vervierfacht.

Daneben gibt es spezielle Einheiten für die Berechnungen von Matrix-Operationen. Von diesen jeweils 512 Byte fassenden Engines sind vier pro Kern vorhanden. Berechnen werden können Daten in FP64 (doppelte Genauigkeit) bis hin zu INT4, also mit geringer Genauigkeit. Auch BFloat16 wird unterstützt.

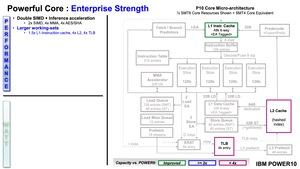

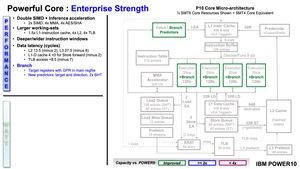

Eine verbesserte Sprungvorhersage und die neue Instruction Set Architecture (ISA) mit einem Fokus auf AI-Anwendungen soll die Effizienz der Kerne verbessern. Hinzu kommt ein auf 2 MB vergrößerter L2-Cache, was eine Vervierfachung gegenüber den POWER9-Prozessoren darstellt. Neben der Möglichkeit acht Threads pro Kern zu verarbeiten, können die Kerne auch anders aufgeteilt werden und sind dann in doppelter Anzahl als SMT4-Kerne anzusehen.

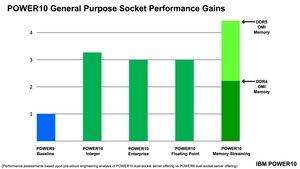

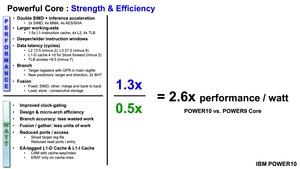

Im Vergleich zu den POWER9-Prozessoren will IBM die Leistung für POWER10 um 30 % für einen einzelnen Kern und um 20 % im Hinblick auf die Single-Threaded-Leistung erhöht haben.

Zu den Verbesserungen in den Kernen gehört also die Verdopplung der SIMDs, aber auch der L1-Instruction-Cache wird um 50 % größer und hat nun eine Kapazität von 48 kB (zuvor 32 kB). Der L1-Data-Cache bleibt mit 32 kB unangetastet. Neben dem L2-Cache wird auch der Translation Lookaside Buffer (TLB) um den Faktor vier größer und kann nun 4.048 Einträge fassen.

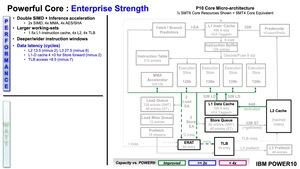

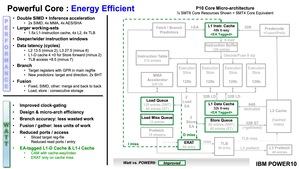

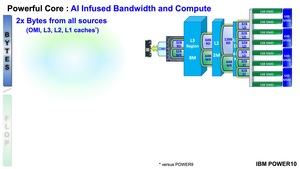

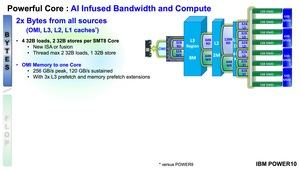

Innerhalb der Cache-Hierarchie gibt es zahlreiche Optimierungen, um die Zugriffszeiten zu reduzieren. Dies betrifft den L1-Data-Cache ebenso wie den L2-Cache und Zugriffe auf den TLB. Im Bereich des AI-Computings sind hohe Speicherbandbreiten wichtig. IBM hat die Bandbreiten, mit denen auf den L1-, L2-, L3-Cache und die per OMI angebundenen Speicher zugegriffen werden kann, verdoppelt. Bei den Caches bezieht sich dies auf Load- und Store-Zugriffe pro Thread. Über das OMI können pro Kern beständig 120 GB/s gehalten werden. Als kurze Burst-Spitzen sind bis zu 256 GB/s möglich. Dazu hat man die Anzahl der Prefetcher für den L3-Cache und Zugriffe auf per OMI angebundenen Speicher verdreifacht.

Um die Effizienz des Prozessors bzw. der Kerne zu erhöhen werden die Instruktionen nicht nur optimiert zusammengeführt und können schneller verarbeitet werden, IBM hat für das POWER10-Design das Clock-Gating verbessert, so dass Bereiche, die nicht benötigt werden, heruntergetaktet oder komplett abgeschaltet werden können.

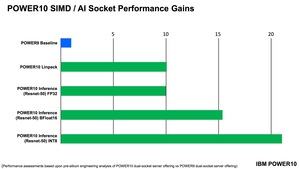

Eine um 30 % höhere IPC-Leistung zusammen mit einer halbierten Leistungsaufnahme führt zu einem um den Faktor 2,6 höheren Leistung/Watt im Vergleich zum POWER9-Kern. Hinsichtlich der AI-Leistung spricht IBM je nach Anwendung und verwendeter Genauigkeit von einem Leistungsplus um den Faktor 10 bis 20 im Verglich zu POWER9.

POWER10-Prozessoren ab 2021

Derzeit befindet sich IBM in der finalen Phase der Entwicklung der POWER10-Prozessoren. Man hat die ersten Chips im Labor und testet diese derzeit. Obige Bilder zeigen einen Wafer mit belichteten POWER10-Chips sowie einen der Chips im Laborequipment.

Mit den ersten Servern, die POWER10-Prozessoren verwendet, wird in der zweiten Jahreshälfte 2021 gerechnet.

Update:

Wir haben bei IBM bezüglich der Unterstützung von NVLink nachgefragt, denn für NVLink 1.0 und 2.0 boten die IBM-Prozessoren eine entsprechende Kompatibilität:

William Stark, Distinguished Engineer bei IBM sagte Hardwareluxx gegenüber:

"IBM and NVIDIA initially partnered to develop NVLINK host-to-GPU attach technology to overcome performance bottlenecks caused by the insufficiency of PCIe Gen3 capabilities. While this provided substantial differentiation relative to PCIe Gen3 and Gen4, the industry accelerated the pace of PCIe development. With the advent of PCIe Gen5, both IBM and NVIDIA determined that PCIe is once again sufficient for eliminating performance bottlenecks in host-to-GPU attach. Therefore a proprietary solution such as NVLINK is no longer a strong differentiator for host-to-GPU attach, and the POWER10 processor will not exploit NVLINK for host-to-GPU attach. The memory-to-host bandwidth afforded by industry standard direct-attach DDR DRAM memory has become a new bottleneck at the system level. We have developed the Open Memory Interface (OMI) as a high bandwidth alternative to overcome this bottleneck, and to provide continued differentiation for Power. As technologies evolve, and concerns of new system level bottlenecks emerge, the we continue to develop new innovations to address them."

Demnach habe man NVLink zusammen mit NVIDIA entwickelt, da PCI-Express 3.0 nicht die notwenige Datenrate zur Verfügung stellen konnte. Mit PCI-Express 4.0 und später PCI-Express 5.0 sei diesen Flaschenhals aber nicht mehr vorhanden und somit sei eine Unterstützung von NVLink durch den Prozessor nicht mehr notwendig.