Werbung

Um die Leistung moderner Prozessoren, Grafikbeschleuniger aber auch SoCs sicherstellen zu können, wird der Interconnect für die Verbindung und den Datenaustausch der einzelnen Komponenten immer wichtiger. An dieser Stelle wollen wir einfach nur einmal auf Intels Omni-Path verweisen und NVIDIA will mit NVLink dem PCI-Express-Interface lebewohl sagen. Nicht direkt zu vergleichen sind diese Technologien natürlich mit dem, was innerhalb eines SoCs passiert, allerdings unterstreichen sie die grundsätzliche Problematik.

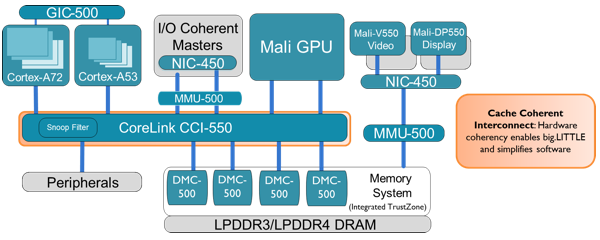

ARM hat mit dem CoreLink CCI-550 nun einen Cache Coherent Interconnect vorgestellt. Mit dem CoreLink CCI-550 will ARM den zukünftigen Anforderungen einer Cache Coherenz zwischen einem LITTLE.big CPU-Cluster, der eigenen Mali-GPUs und weiteren Komponenten eines SoC gerecht werden. Wem das Heterogeneous Computing nun recht wenig sag, dem legen wir unseren Artikel zu AMDs HSA-Technologie nahe, wo die grundsätzlichen Thematiken erläutert werden. Es geht darum den Datenaustausch und die Datenbasis einer oder mehrerer Berechnungen auf möglichst viel Compute-Hardware zu bringen. Dies soll die Programmierung vereinfachen und die Leistung der Aufgaben verbessern. Der CoreLink CCI-550 ist eine nur logische Erweiterung zu den bisherigen Anstrengungen innerhalb der Cache-Coherent-Interconnect-Familie bei ARM.

Der CoreLink CCI-550 bietet die Möglichkeit bis zu sechs ACE-Interfaces (LITTLE.big-Cluster, Mali-GPUs oder andere Komponenten) anzubinden. Mit einer Bandbreite von bis zu 50 GB pro Sekunde sieht sich ARM hinsichtlich der zukünftigen Anforderungen gerüstet. Selbst aufwendige Multi-Tasking-Prozesse sollen sich damit über die Systeme verarbeiten lassen. 4K-Displays, egal ob intern oder extern, sollen auf Tablets und Smartsphones zukünftig ebenfalls kein Problem mehr sein. Natürlich rückt ARM die Zusammenarbeit aus eigner LITTLE.big-Architektur und Mali-GPU in den Fokus, um beispielsweise eine Echtzeit-Bildstabilisierung in hohen Auflösungen zu ermöglichen oder aber nennt komplexe Kontext- und Inhalt-Suchen als Anwendungsbeispiel für die Notwendigkeit des Heterogeneous Computing bzw. des neuen Cache Coherent Interconnect.

Bis wir erste Umsetzungen der Lizenznehmern bei ARM sehen, die auf den CoreLink CCI-550 Cache Coherent Interconnect setzen werden, werden allerdings noch mindestens zwöf Monate vergehen. Vor Ende 2016 wird es also keine konkreten Produkte auf dem Markt geben.

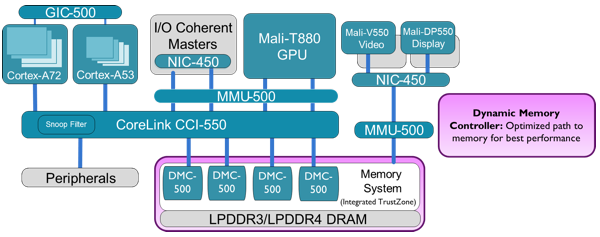

[h3]CoreLink DMC-500 Dynamic Memory Controller[/h3]

In diesem Zusammenhang ebenfalls erwähnt sei der neue CoreLink DMC-500 Dynamic Memory Controller. Dieser soll die dazu notwendige Anbindung des Arbeitsspeichers sicherstellen. Ab Ende des kommenden Jahres sollen damit SoCs möglich sein, die Arbeitsspeicher mit Geschwindigkeiten von LPDDR3-2133 und LPDDR4-4267 unterstützen. Diese sind natürlich als fester Teil des SoC eingebunden und bieten jeweils einen Channel. ARM zeigt ein mögliches Design mit vier Controllern, die dann in einem Quad-Channel-System arbeiten würden. Mit dem CoreLink DMC-500 Dynamic Memory Controller will ARM die Bandbreite um 27 % erhöhen und die Latenzen um 65 % verringern (im Vergleich zum Vorgänger CoreLink DMC-400).