Holt

Legende

- Mitglied seit

- 05.07.2010

- Beiträge

- 31.779

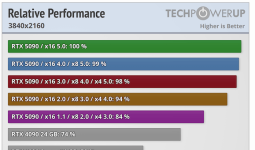

Das ist möglich, aber es ist auch möglich, dass es wie bei Rocket Lake sein wird und es neben den 16 PCIe Lanes für die Graka auch gleich 4 für einen M.2 Slot mit dem neusten, schnellsten PCIe Lane geben wird. Es ist am Ende halt das Henne Ei Problem und dies kann nur überkommen werden, wenn beide Seite etwa zeitgleich mit der ja immer recht langwierigen Entwicklung loslegen, auch wenn dies dazu führt, dass es am Ende beim Marktstart so aussieht, also ob einer vorlegt und die andere Seite nachzieht.Wenn das wieder kommen würde mit nächster Generation, dann wäre es wie bei Alderlake/Raptorlake.

Dabei haben beide Seite am Ende ein Interesse daran die neusten Schnittstellen zu bringen. Wie wissen nicht wie viele Leute sich damals AMD X570 Boards wegen PCIe 4.0 gekauft haben oder AM5, weil es schon PCIe 5.0 Lanes auch für M.2 Slots bot. Ich selbst habe mir damals einen Phenom II X6 gekauft, weil die AMD SB850 eben schon 6 SATA 6Gb/s Ports bot, als Intel diese noch nicht hatte.

Dann wäre es aber x16 und nicht x8 und damit nicht wie du es vorher geschrieben hast, "wieder eine Beschneidung auf PCIE6 x8 vorstellen". Ist es für dich so schwer sich einzugestehen, dass du dich geirrt hast? Dabei sollte dies für dich eine Warnung sein, entweder deiner Erinnerung oder deinen Quelle nicht einfach so zu vertrauen, sondern diese künftig zu hinterfragen. Es gibt Leute die meinen es wäre ein Zeichen von Schwäche Fehler und Irrtümer zuzugeben, aber es ist ein Zeichen von Dummheit und Arroganz es nicht zu tun, denn jeder irrt sich mal und macht mal einen Fehler. Wer für sich in Anspruch nimmt da eine Ausnahme zu sein, ist bei mir ganz unten durch und vermutlich zu dumm dazulernen zu können, weshalb er es gar nicht erst versucht.Dann wäre es wieder.

wurde aber zurück abgewickelt

wurde aber zurück abgewickelt

Eher aber so als technologische Kunst

Eher aber so als technologische Kunst