HWL News Bot

News

Thread Starter

- Mitglied seit

- 06.03.2017

- Beiträge

- 114.215

... weiterlesen

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: this_feature_currently_requires_accessing_site_using_safari

Entweder habe ich einen Denkfehler oder...

32MB pro Chiplet, was spricht dann gegen einen 8Core CCX... irgendwie verstehe ich nicht, wie man dadurch jetzt schon ableiten kann, dass es wieder genau wie bei Zen 1 sein wird.

Hoffentlich hat AMD dann das Augenmerk auf die Optimierung der bestehenden CCX gelegt, weil sie keine Arbeit ins Ummodeln von 4 auf 8 Kerne pro CCX stecken mussten. Eine Steigerung von mehr als 5% IPC wäre super

Was von irgendwelchen Tool bei irgendwelchen Prototypen ausgelesen wird, muss noch lange nicht stimmen und wenn ich mit erinnere wie große der zentrale I/O Chip und wie klein die Chiplets sind

Die I/O-Die ist ca. doppelt so groß wie Zeppelin.Und was steckt denn alles in dem I/O Chip, der ja gut und gerne die Größe eines Zeppelin Dies hat?

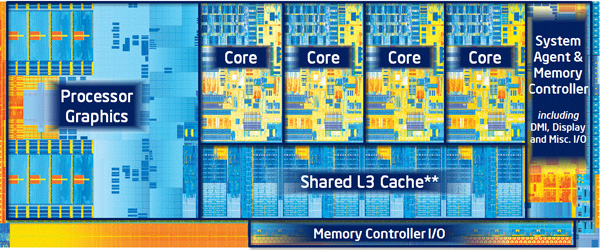

L3 auslagern ergibt keinen Sinn, die Kerne sollen schnell darauf zugreifen können!Nicht vielleicht doch der L3 Cache auf den dann alle Kerne gleich fast gut zugreifen könnten, wenn der zentral gehalten wird?

Die I/O-Die ist ca. doppelt so groß wie Zeppelin.

L3 auslagern ergibt keinen Sinn, die Kerne sollen schnell darauf zugreifen können!

Ausserdem wäre die I/O-Die für 256MB L3 eindeutig zu klein

4MB pro Kern wären es aber immer, egal ob 4er oder 8er CCXntweder es bleibt bei 4er CCX mit jeweils 16MB dann oder es wird 4MB pro Kern.

Weil es einfach so ist, das ist allgemein bekannt!Wieso sollte "das I/O-Zeug nicht 1:1 geshrinkt werden" können?

Was soll man da bitte geschafft haben?Gamerkind, und wie schafft man dieses angeblich Unmögliche bei den 7nm ARM Server CPUs und SoCs für Mobilgeräte oder bei 7nm GPUs?

Somit könnte ein L3 Drive in greifbare Nähe rücken.

Alle nicht, die Chiplets werden wohl zumindest die Stromversorgung noch direkt vom Sockel bekommen.Immerhin müssen alle AM4 Pins an den I/O Chip

unl34shed, die Strukturgrößen des Prozesses haben mit den BGA Pads doch nun gar nichts zu tun, ...

Die BGA Pads sind unten an der CPU und verbinden diese mit dem Sockel, die gibt also nur die Größe der Trägerplatine der CPU und des Sockels vor und hat nichts damit zu tun wie die Abstände der Verbindungspunkte zwischen dem Die und der Trägerplatine sind.Seine Bedenken, das man am I/O Chip nicht genug Fläche hat um alles anzubinden kann ich aber schon nachvollziehen.

Mehr als der Sockel Pins hat plus denen der IF Anbindung des Chiplets auch nicht, sofern AMD überhaupt bei den AM4 Zen2 auf diese Technik setzen wird, dies ist ja noch gar nicht bekannt.Immerhin müssen alle AM4 Pins an den I/O Chip und zusätzlich noch die Chiplets angebunden werden. Da kommt schon was zusammen.

Wenn man sich ansieht wie hoch die Leistungsaufnahme der IF und des Uncore ist, dann denke ich schon das es sich technisch gelohnt hätte den I/O Chip auch in 7nm zu fertigen:Die Hauptgründe werden aber wohl a) die Verträge mit GloFo und b) die nicht lohnenswerte Skalierung des I/O Die auf 7nm sein.

Bei EPYC 7601 macht unter Last die Leistungsaufnahme der Kerne gerade die Hälfte der gesamten Leistungsaufnahme aus und nur die Kerner werden durch die 7nm effizienter, der I/O Chip könnte daher bei Rome durchaus die Hälfte der Leistungsaufnahme ausmachen und damit würde es sich sicher lohnen diese Leistungsaufnahme ebenfalls durch ein Fertigungsverfahren zu senken welches eine bessere Effizienz ermöglicht. Bei der nächsten dürfte dies dann wohl auch gemacht werden.

Eben und da ist ein 14nm I/O Chip billiger, zumal die Schaltungen ja bisher auch schon für den 14nm Prozess von GF im Zeppelin Die vorliegen, die einzelnen Funktionsgruppen müssen also nicht neu designt, sondern nur neu arrangiert werden.Man sollte sich bewusst sein, das AMD derzeit möglichst kosteneffizient versucht CPUs zu bauen.

Ja:Hab ich was anderes behauptet?

Das trifft eben bei CPUs nur auf die Größe der Trägerplatine zu.Holt, der limitieren der Faktor sind die BGA Pads bzw. Balls. Die können nicht beliebig verkleinert werden.

Und wieder wirfst Du die Verbindung des Dies mit der Trägerplatine und die der Trägerplatine mit dem Sockel durcheinander.Die BGA Pads bzw. ihre Anzahl geben aber die Chipgröße vor, da es sich (wie seit Jahren Standard) wohl wieder um einen Flip Chip handelt.