Der X3D, der

5700X3D, gegenüber dem da aufgelisteten 285k, ist cherry picking?! (es wird nicht besser, liebes Publikum... es wird nicht besser

)

Dein Text "Aber: Man kann es als grobe Orientierung für Delta zwischen A & B verwenden" ->

-> Pass uff Atze, nach so beschriebener Metrik, für dein... Orientierungsdelta, kannst du dafür erfolgreich auch den internen Bench von WinRar nehmen.

Was ist das für Rumpalavern wieder? Hat er dich angesteckt?

Warum wieder der X3D?

Ist das Intel vs AMD so wichtig?

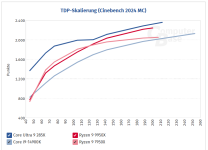

Es geht doch nur um Cinebench und meiner Meinung das man das ohne X3D relativ gut als Indikator verwenden kann um eine Schlussfolgerung zu ziehen.

Lass mal den X3D weg und das INTEL VS AMD. Ich bin weder noch und habe beides zuhause.

Die Metrik hat jahrelang so ungefähr gestimmt. Die Metrik sagt nicht das du jetzt 120FPS anstelle von 60 weil die Punktezahl doppelt ist. Davon war nie die rede sondern die Wahrscheinlichkeit das CPU A mit 600 Punkte und B mit 800 Punkte hier B in Games gleich oder besser abschneidet ist gegeben.

Das kannst du beim 5700X3D auf den 5800X3D auch beobachten oder auf den 7800X3D oder 9800X3D. Das jede CPU mehr Score erreicht und dadurch mehr Gaming Leistung.

Was versuchst du zu beweisen?

Oder was ist hier dein Anliegen?

Cinebench als Test ist nicht Fisch nicht Fleisch, deshalb eignet er sich nicht als absoluter Anwendungsbenchmark, aber auch nicht als absoluter Gaming Benchmark.

Wenn man es so sehen will ist es ein Mittelwert aus mehreren Disziplinen und für absolute Resultate nicht geeignet nur relative, außer du willst für Rendering die beste geeignete CPU haben.

Aber es gibt kaum allgemein gültige Benchmarks die auf alle Games reflektiert werden können, für mich ist Cinebench einer der aber am nächsten kommt eine relative Performance für Gaming einzuschätzen.

Da mir die Absolute Gaming Leistung total egal ist

schau ich auf etwas anderes und ich spiele keine sehr speziellen spiele, deshalb reicht mir das Cinebench Rating als ungefährer Indikator und bisher wurde ich nie enttäuscht.

Für das CS Kiddie oder Fail4Duty Gamer sind halt die FPS in eben jenen Games relevant soviel wie geht.

Da kann man aber auch nie ohne entsprechende Benchmarks in diesen Games absolute Kaufempfehlungen geben. Den oh wunder die X3D der AM4 waren plötzlich langsamer oder nur geradeso gleich so schnell wie die neuen Non X3D AM5.

Das ist für mich total irrelevant solange ich genug FPS habe die gut Spielbar sind.

Deshalb ist mir Egal ob ich in Game XY nicht die besten FPS habe solange ich Mittelwert entsprechend gute werte habe.

Heutzutage zählt übrigens nicht der Hersteller sondern das Ziel das ich mit der Hardware verfolge.

Wenn ich sage ich möchte eine allgemeine nicht spezifische Leistung ermitteln ist der Cinebench schon geeignet, aber er berücksichtig halt nicht spezielle Präferenzen.

Ich finde halt man muss halt schauen, ein X3D lohnt sich nicht in jedem Fall. Es sei denn er ist preiswert, wenn man nur eine 5060TI als Grafikkarte hat kann man mit einer X3D nicht viel anfangen außer man will Quake 3 mit 999FPS @480P zocken oder so. Weil man mit so einer Bumbs Grafikkarte gar nicht das Potential des X3D ausschöpfst.

Aber da sind wir hier schon bei Offtopic.

)

)