Werbung

Mit der "Zen"-Architektur will AMD wieder an gute alte Zeiten anknüpfen und geht in Sachen Design sozusagen einen Schritt zurück. Bisher sind nur einige vereinzelte Details zur Architektur bekannt, die zum Beispiel von bis zu 16 CPU-Kernen ausgehen oder detaillierte Strukturen zum Cache, der Anbindung des Arbeitsspeichers und der integrierten Grafikeinheit beschreiben.

Nun ist ein Blockdiagramm aufgetaucht, welches die "Zen"- gegen die "Excavator"-Architektur vergleicht. Darin ist zu erkennen, dass AMD die Abkehr vom CPU-Modul, welches wiederum eine Art Multi-Core-Design verwendet, zum monolithischen Block offenbar weiter vorantreibt. Sowohl die Decode- als auch die Integer-Scheduler arbeiten nicht mehr in zwei Modulen zusammen, sondern sind eben als einzelner Block ausgeführt. Für Integer-Berechnungen stehen nicht mehr acht sondern nur noch sechs Pipelines zur Verfügung. Fließkommaberechnungen erfolgen nicht mehr in in zwei FMAC (Fused Multiply Accumulatoren) mit 128 Bit, sondern arbeiten nun mit einer Genauigkeit von 256 Bit.

MAC-Operationen sind Befehle, bei denen zwei Faktoren multipliziert und das entstehende Produkt zu einem weiteren Summanden addiert werden. Bei der MAC-Operation kann eine Verbesserung der Genauigkeit im finalen Ergebnis erzielt werden, in dem die notwendige Rundung erst am Ende der MAC-Operation ausgeführt wird und die Zwischenergebnisse intern mit voller Auflösung ohne Rundungen durchgeführt werden. Diese werden dann FMAC genannt, benötigen aber breitere Datenpfade und bedingen auch einen erhöhten Hardwareaufwand. Den Weg zu immer komplexeren Compute-Anwendungen bedingt auch eine immer größere Genauigkeit bei den Berechnungen.

Der dazugehörige L2-Cache wird pro Kern nur noch 512 kByte groß sein, während dieser bei "Excavator" noch 2 MB fassen konnte. Da die neuen Kerne die entsprechenden Daten aber schneller berechnen sollen, wird auch kein derart großer Cache mehr benötigt. Ähnlich ging Intel bei der "Haswell"-Architektur vor. Vermutlich wird auch AMD bei der "Zen"-Architektur auf einen großen L3- oder L4-Cache setzen, der die Daten zusammenfasst und zwischen den einzelnen Kernen austauscht. Daran angebunden findet sich dann eine möglichst schnelle Anbindung an den Arbeitsspeicher oder das PCI-Express-Interface wieder.

Update:

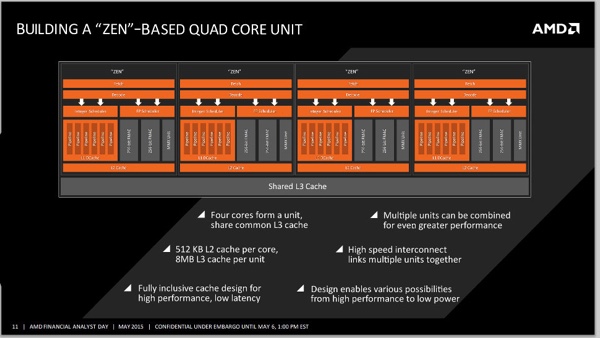

Im Forum von Planet3DNow! ist eine weitere Folie aufgetaucht, die eine komplette Unit an "Zen"-Kernen zeigt. Diese Unit besteht aus vier "Zen"-Kernen, welche sich einen 8 MB großen L3-Cache teilen. Der L2-Cache ist wie gesagt 512 kByte groß. Diese Quad-Core-Unit stellt den größten möglichen Block eines CPU-Designs dar. Es ist aber möglich mehrere dieser Units zu kombinieren. Bisher wird von maximalen 16 Kernen, also vier Units ausgegangen. Untereinander sind diese dann über ein GMI (Global Memory Interconnect) verbunden. Diese Verbindung wird vermutlich auch eingesetzt, um den High Bandwidth Memory an die CPU/GPU anzubinden.

Eine Unit muss aber nicht zwangsläufig die vollen vier Kerne verwenden. So sind auch CPU-Designs denkbar, die "nur" über zwei Kerne verfügen.

2. Update: Neue Roadmaps

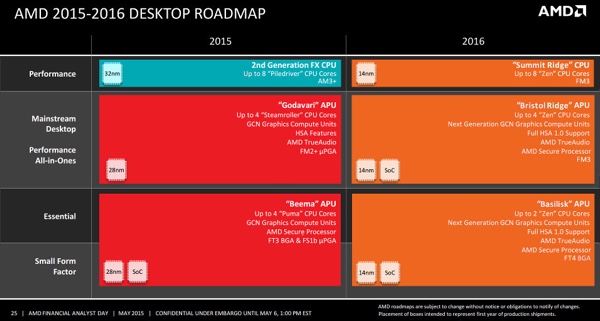

Zwei weitere Folien sind aufgetaucht, auf denen die Roadmaps für Mobile- und Desktop-Prozessoren aufgeführt sind. Demnach erwartet uns für 2016 eine neuer Performance-Prozessor von AMD - ein Feld, das man aktuell Intel überlassen hat. Die "Summit Ridge" getaufte CPU wird in 14 nm gefertigt und verwendet acht "Zen"-Kerne. Platz findet der Prozessor im Sockel FM3. "Summit Ridge" kommt gänzlich ohne GPU aus.

Bei den APUs soll "Bristol Ridge" die Kohlen aus dem Feuer nehmen. Dort werden bis zu vier "Zen"-Kerne angeboten, die im Zusammenspiel mit einer GPU auf Basis der nächsten Generation der GCN-Architektur arbeiten. Als erste APU soll "Bristol Ridge" vollständig zu HSA 1.0 kompatibel sein. Unterstützt wird natürlich auch TrueAudio und AMD Secure Processor. Auch "Bristol Ridge" findet auf dem FM3-Sockel Platz. Im unteren Bereich angesiedelt sein soll "Basilisk" mit bis zu zwei "Zen"-Kernen. Auch hier werden die nächste Generation der GCN-Architektur, HSA 1.0, TrueAudio und AMD Secure Processor angeboten. "Basilisk" wird nur als BGA-Version angeboten werden.

Bei den Mobile-Prozessoren finden wir ein paar der eben genannten Designs wieder. "Bristol Ridge" deckt dabei den oberen Performance-Bereich ab, dessen TDP bei 15 bis 35 W liegt. Auch "Basilisk" wird in der Mittelklasse erwähnt und soll mit 5 bis 15 W auskommen. Im Ultra-Low-Power-Segment wird AMD "Styx" anbieten. Dabei soll nicht mehr die "Zen"-Architektur, sondern die ebenfalls in der Entwicklung befindliche "K12"-Architektur zum Einsatz kommen. Bis zu zwei dieser Kerne sollen in "Styx" arbeiten, alle weiteren Details kennen wir bereits von den schnelleren Modellen mit "Zen"-Architektur. Die Leistungsaufnahme wird mit etwa 2 W angegeben.