Werbung

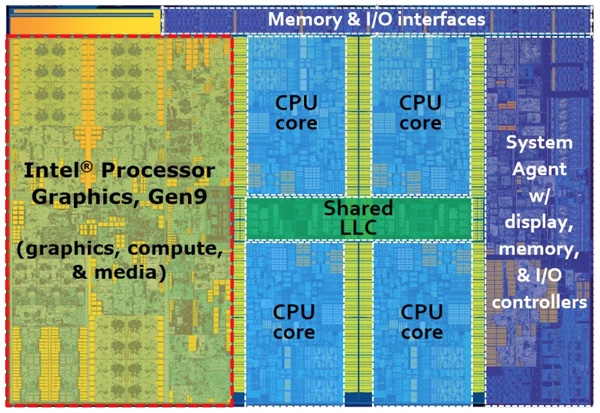

Bisher hat sich Intel mit Details zur Architektur der Skylake-Prozessoren zurückgehalten und das obwohl mit dem Core i7-6700K und Core i5-6600K bereits die ersten beiden Desktop-Prozessoren vorgestellt wurden und am Markt erhältlich sind. Ab heute nun findet in San Francisco das alljährliche Intel Developer Forum statt, von dem wir uns auch einige Details zu den Änderungen bei Skylake erwarten. Ein Whitepaper zur Compute Architektur der Intel Prozessor Graphics Gen9 wurde nun veröffentlicht, auf das wir in der Folge etwas genauer eingehen wollen. In den beiden bereits vorgestellten Skylake-Prozessoren hört die Grafikeinheit auf den Namen Intel HD Graphics 530.

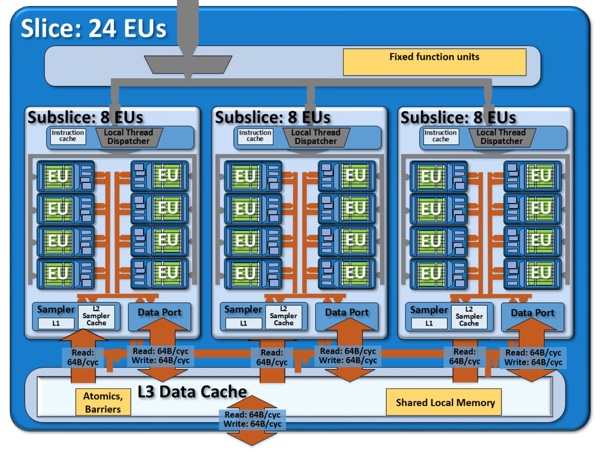

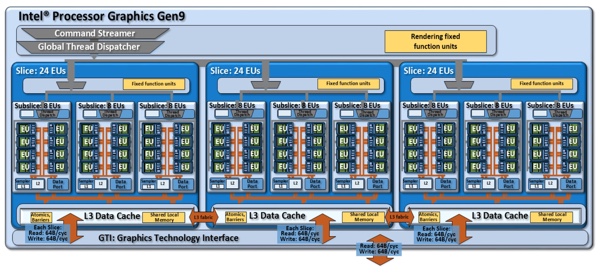

Zunächst ein mal bleibt vieles so, wie wir es bereits aus der Graphics Gen8 kennen. Intel hat allerdings einige Änderungen in den internen Strukturen und Verbindungen vorgenommen, was die Gen9 flexibler machen soll. So ist es nun möglich, eine Konfiguration zu erstellen, in der drei Slices und wiederum drei Subslices arbeiten, was insgesamt 72 EUs in einem Skylake-Prozessor ermöglicht. Zuvor waren dies bei Broadwell maximal 48 und damit ein Drittel weniger. Außerdem hat Intel die Takt-Domains sowie das Power Gating optimiert, wodurch die Gen9 noch einmal deutlich effizienter werden soll. Besonderer Fokus soll dabei auf einer niedrigen Leistungsaufnahme beim Abspielen von verschiedenen Codecs gelegt worden sein.

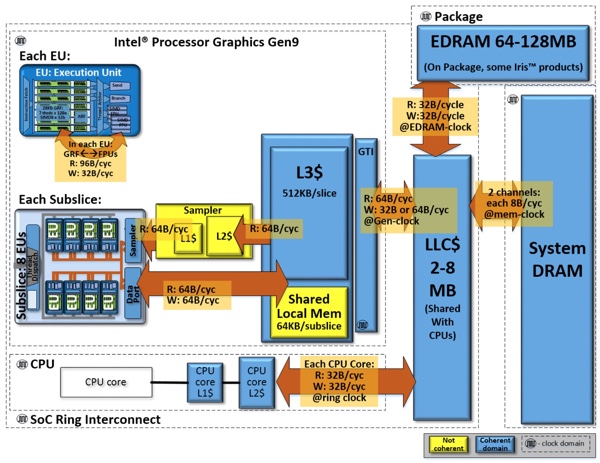

Neben dem breiteren und effizienteren Aufbau der Graphics Gen9 hat Intel wie gesagt vor allem interne Architektur-Veränderungen vorgenommen – hier vor allem bei der Speicher-Hierarchie. Durch neue Caching-Technologien soll die Schreibleistung des coherenten Shared Virtual Memory (SVM) durch den Last Level Cache (LLC) deutlich beschleunigt worden sein. Außerdem wurde der L3-Cache auf 768 kByte vergrößert, von denen 512 kByte Application Data zugewiesen sind. Um die Anfragen an die Caches und Speicher beschleunigen zu können, hat Intel die Request Queues verbreitert. Damit kann die Anzahl an Anfragen an den Speicher erhöht werden, was die Latenzen verringern und die Bandbreite erhöhen soll.

In der Graphics Gen9 fungiert der optionale EDRAM als Memory-Side Cache zwischen dem LLC und DRAM. Zudem wurde der Speichercontroller der EDRAM in den System Agent übertragen, wo er eine direkte Verbindung zum Display Controller besitzt. Damit verkürzen sich die Wege und Zeiten zur Darstellung auf dem Display und ermöglicht wird ebenso eine weitere Stromsparoption durch das Mehrfache darstellen eines Frames direkt aus dem EDRAM heraus, ohne dass die GPU diesen erneut berechnen muss. Texturen können nun außerdem im NV12 YUV Format hinterlegt werden, was die Zusammenarbeit zwischen Compute-APIs und den sogenannten Media Fixed Function Units beschleunigen soll.

Auf Seiten der Compute-Funktionen hat sich ebenfalls einiges getan. So wird das sogenannte Preemption nun auf Thread Level unterstützt, so dass Compute Threads bereits während der Ausführung vorausberechnet, gestoppt und später fortgesetzt werden können. Intels Graphics Gen9 unterstützt nun außerdem 32 Bit Float Atomics. Dabei handelt es sich um einen Verbund von Einzeloperationen, der als logische Einheit betrachtet werden kann und nur als Ganzes erfolgreich ablaufen oder fehlschlagen. Unterstützt werden die Operationen Min, Max sowie Compare und Exchange.

Bereits erwähnt haben wir den Umstand, dass sich am Aufbau der einzelnen Execution Units (EU) sowie den größeres Subslices und Slices wenig bis gar nichts getan hat. Intel ermöglicht nur den besagten Aufbau von drei Slices und drei Subslices, so dass Skylake auf insgesamt 72 EUs kommen kann. Ein entsprechendes Produkt in dieser Konfiguration gibt es bislang aber noch nicht.

Nominell ändert sich an der Leistung einer Konfiguration mit 24 EUs nichts. Sowohl die Graphics Gen8 als auch die Gen9 können in dieser Konfiguration 168 Threads in 5.376 Instanzen bearbeiten. Der Shared L3-Cache ist bei Gen9 allerdings fixe 512 kByte groß, während es bei der Gen8 noch 384 kByte im Minimum waren. Die Größe des LLC kann nun ebenfalls breiter variieren und reicht von 2 bis 8 MByte, während es zuvor noch 4 bis 8 MByte waren. Die reine Rechenleistung ist zwischen Gen8 und Gen9 auf dem Papier identisch. Intel spricht von 384 FLOPS/Cycle bei 32 Bit Float, 96 FLOPS/Cycle bei 64 Bit Double Float und 192 IOP/Cycle bei 32 Bit Integer IOPS.