Werbung

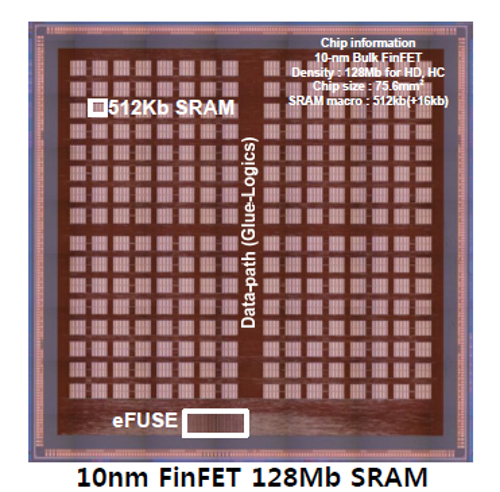

Gerade erst kann von einer Massenfertigung in 14/16 nm gesprochen werden, da beginnen die großen Halbleiterhersteller damit konkrete Zahlen zum nächsten Schritt zu nennen. Wie immer beginnt man natürlich mit recht einfachen Strukturen, da diese in einer neuen Fertigungstechnologie zunächst einmal weniger Probleme aufwerfen können. Auf der Solid-State Circuits Conference (ISSCC) sprach Samsung nun über die 10-nm-FinFET-Fertigung für 128-MBit-SRAM-Chips.

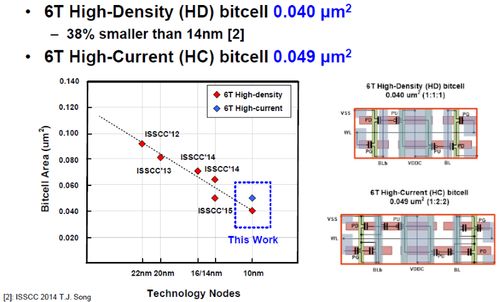

Laut Samsung sind die neuen Chips 38 % kleiner als die in 14 nm gefertigten Chips. Die Chipfläche beträgt 0,040 µm2 im Vergleich zu 0,049 µm2. Da SRAM-Speicherchips auch ein Bestandteil eines SoC sein können und hier bis zu 30 % Fläche einnehmen, wirkt sich dieser auf den im ersten Blick recht kleinen Unterschied schnell relativ deutlich aus. Die kleineren Strukturen machen natürlich auch deutlich niedrigere Spannungen möglich. Samsung spricht von 45 mV in der High-Current- und 130 mV in der High-Density-Variante. Man habe aber noch einige Hürden zu nehmen, um von einer Serienreife zu sprechen.

Dabei kann es sich Samsung nicht verkneifen einige Vorteile gegenüber der Konkurrenz und hier vor allem TSMC herauszustreichen. Dazu gehört der Fakt, dass Samsung neben den eigentlichen FinFETs auch die Interconnects deutlich verkleinert hat. TSMC verwendet bei seinem 16-nm-FinFET-Prozess weiter ein Standardverfahren aus dem 20-nm-Prozess. Dies erklärt auch die Größen- (und vermutlich auch Verbrauchsunterschiede) zwischen den A9-SoCs des iPhone 6s und iPhone 6s Plus. Eine detaillierte Analyse hat hier ergeben, dass der A9 von TSMC auf 105 mm2 kommt, während das Modell von Samsung nur 96 mm2 misst. Bei gleicher FinFET-Fertigung sollte der Unterschied eigentlich nicht so groß sein. Die größeren Interconnects bei TSMC könnten den Größenunterschied aber zumindest teilweise erklären. Samsung verwendet hingegen in seinem 14-nm-Prozess die gleichen Strukturgrößen für FinFETs und Interconnects. Beim 10-nm-Prozess will Samsung ebenso vorgehen, macht aber keine definitiven Größenangaben.

Aus dem von Samsung veröffentlichten Papier geht nicht hervor, welche Einsparungen hinsichtlich der Leistungsaufnahme möglich sind. Ebenso ist nicht abzusehen, ob eine 10-nm-FinFET-Fertigung für SRAM Rückschlüsse auf eine solche von kompletten SoCs zulässt. Der einzige Hinweis auf entsprechende Werte ist die Aussage von "ähnlichen Leistungssteigerungen" gegenüber dem 14-nm-Prozess.