Werbung

Die JEDEC Solid State Technology Association hat die finalen Spezifikationen für den LPDDR6-Standard veröffentlicht. LPDDR steht für Low Power Double Data Rate und dieser Speicher kommt vor allem im Zusammenspiel mit schnellen SoC im Notebook-, Smartphone- und Tablet-Bereich zum Einsatz.

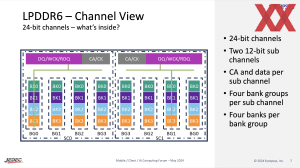

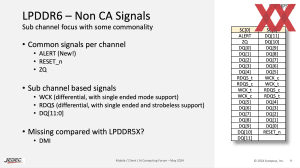

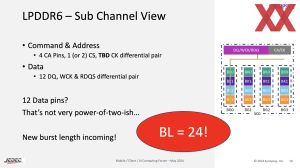

Hinsichtlich des Aufbaus des Speichers wird sich im Vergleich zum Vorgänger gar nicht so viel tun. Auch LPDDR6 wird zwei Sub-Kanäle verwenden, um eine möglichst hohe Speicherbandbreite zu erreichen. Pro Sub-Kanal ist der Datenbus aber nur noch 12 statt wie bisher 16 Bit breit. Somit kämen wir auf 24 Bit je Die. Die offene Frage ist, ob LPDDR6 somit auf zwei Dies je Chip geht, um auf einen 48 Bit je LPDDR6-Chip zu kommen.

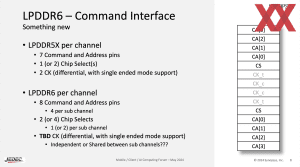

Seit LPDDR4 war der CA-Bus (Command/Address-Bus) 6 Bit breit, mit LPDDR6 wird dieser nun auf 4 Bit verkleinert. Der CA-Bus ist das Steuerzentrum des DDR-Speichers: Er bestimmt, was der Speicher tun soll, wo er es tun soll und wann. Ohne ihn gäbe es keine gezielte Kommunikation zwischen Controller und Speicherzellen.

LPDDR6 soll Datenraten von 8.800 bis 17.600 MT/s erreichen können. Bei LPDDR5X sind wir inzwischen bei 10.700 MT/s angekommen. LPDDR6 ist somit die Ablöse und wird die Transferrate des Speichers somit weiter steigern.

Alle bekannten Speicherhersteller, dazu gehören Micron, Samsung und Sk Hynix, werden zu gegebener Zeit LPDDR6 anbieten können. Bisher hat sich aber noch kein Hersteller zu einem groben Zeitraum geäußert.

Update:

Gestern fehlten uns noch einige Informationen, die unsererseits auch zu Fehleinschätzungen führten. Dankenswerterweise verwies uns smalM auf eine 2024 von Synopsys verteilte Präsentation zu LPDDR6, die alle wichtigen technischen Merkmale enthält.

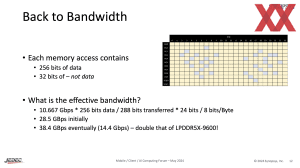

Bereits erwähnt haben wir, dass der Datenbus pro Sub-Kanal von 16 auf 12 Bit verschmälert wird. Im Gegenzug wird aber auch die Burst-Länge verlängert, so dass am Ende doch eine höhere Bandbreite erreicht wird. Die Größe des Sub-Channel-Data-Packets beträft 288 Bit, von denen 256 Bit Daten und 32 Bits Metadaten bzw. RAS-Funktionen sind.

Die effektive Bandbreite für LPDDR6 kann so zum Beispiel 28,5 GBit/s betragen – 10.667 GBit/s * 256 Bit (Daten) / 288 Bit * 24 Bit / 8 Bit = 28,5 GBit/s. Zum Vergleich: Ein LPDDR5X-10700 kommt eben auf 10,7 GBit/s.

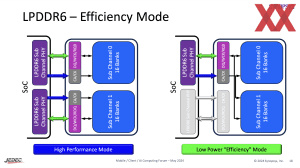

Zudem unterstützt LPDDR6 einen Efficiency Mode. Bei diesem wird einer der beiden Sub-Kanäle abgeschaltet und auf beide Bänke des LPDDR6 wird über einen der Kanäle zugegriffen. Dies reduziert natürlich die Bandbreite, spart aber Leistungsaufnahme ein. Somit bietet LPDDR6 dann doch deutlich Änderungen gegenüber LPDDR5(X). Diese führen dazu, dass LPDDR6 einerseits eine höhere Leistung wird erreichen können, dabei aber auch effizient sein kann. Allerdings bedeutet diesen Umstellungen auch, dass die Speichercontroller neue Funktionen beherrschen müssen.